Catalog

1. Description of successive approximation algorithm

1. Description of successive approximation algorithm

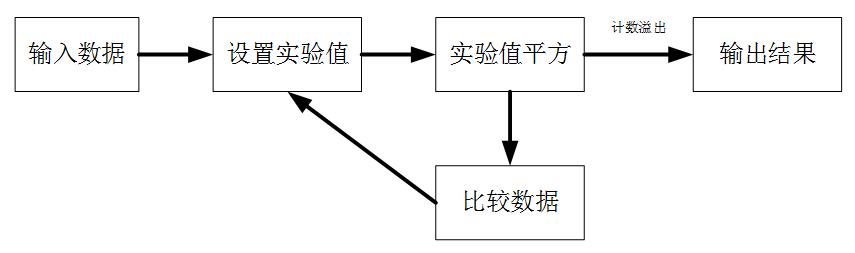

The flow of successive approximation algorithm is shown in Figure 1. First, input data[7:0], then set the experimental value d [3:0] and the determined value d [3:0], and then set each position 1 (e.g. d [3] to 1) in order from high to low, and then compare the experimental value with the input data. If the square of the experimental value is greater than the input value (d [Z ^ 2 > data), then this bit is 0 (d [Q [3] is 0). , otherwise ((D ﹐ Z ^ 2 ≤ data)), this bit is 1 (D ﹐ Q [3] is 1); this bit is iterated to the last bit.

It can be seen that n/2 iterations are required for n-bit data, and n/2 cycles are required for each calculation period.

The Figure1 block diagram of successive approximation algorithm

2.Verilog implementation

3.Testbench To write

//-------------------------------------------------------------------------------- `define d_w 8 `define q_w `d_w / 2 `define r_w `q_w + 1 //-------------------------------------------------------------------------------- module tb_sqrt; //-------------------------------------------------------------------------------- // Inputs reg clk; reg rst; reg i_vaild; reg [`d_w-1:0] data_i; // Outputs wire o_vaild; wire [`q_w-1:0] data_o; wire [`r_w-1:0] data_r; //-------------------------------------------------------------------------------- // Instantiate the Unit Under Test (UUT) sqrt_1 #( .d_width ( `d_w-1 ), .q_width ( `q_w-1 ), .r_width ( `r_w-1 ) ) uut ( .clk ( clk ), .rst ( rst ), .i_vaild ( i_vaild ), .data_i ( data_i ), .o_vaild ( o_vaild ), .data_o ( data_o ), .data_r ( data_r ) ); //-------------------------------------------------------------------------------- initial begin // Initialize Inputs clk = 0; rst = 1; // Wait 100 ns for global reset to finish #100; rst = 0; // Add stimulus here end always #5 clk = ~ clk ; reg [`d_w:0] cnt ; reg [31:0] a ; //-------------------------------------------------------------------------------- always@(posedge clk or posedge rst) begin if(rst) begin i_vaild <= 0; data_i <= 0; cnt <= 0; end else if(cnt < 10) begin i_vaild <= 1; data_i <= {$random} % 255; cnt <= cnt + 1; end else begin i_vaild <= 0; data_i <= 0; cnt <= cnt; end end //-------------------------------------------------------------------------------- endmodule

The statement data I < = {$random}% 255; generates a random number from 0 to 255 for testing.

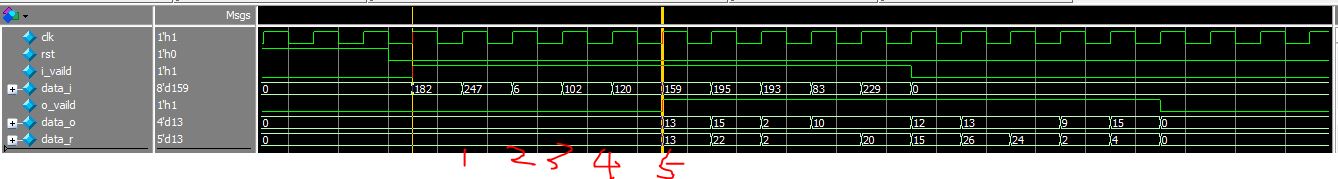

The simulation results are shown in Figure 2. The calculation period is four clock periods, with input data, root result, data and remainder data.

The Fig. 2 simulation results