1. Dflip-flop

module top_module( input clk, input d, output reg q); always@(posedge clk)begin q <= d; end endmodule

2. Dflip-flops

Create 8 D triggers. All DFF s shall be triggered by the rising edge of clk.

module top_module (

input clk,

input [7:0] d,

output [7:0] q

);

always@(posedge clk)begin

q <= d;

end

endmodule

3. DFF with reset

Create 8 D flip flops with high level active synchronous reset. All DFF s shall be triggered by the rising edge of clk.

module top_module (

input clk,

input reset, // Synchronous reset

input [7:0] d,

output [7:0] q

);

always@(posedge clk)begin

if(reset)

q <= 8'b0;

else

q <= d;

end

endmodule

4. DFF with reset value

Create 8 D flip flops with high level active synchronous reset. The trigger must be reset to 0x34 instead of zero. All DFF s shall be triggered by negative edge CLK

module top_module (

input clk,

input reset,

input [7:0] d,

output [7:0] q

);

always@(negedge clk) begin

if(reset)

q <= 8'h34;

else

q <= d;

end

endmodule

5. DFF with asynchronous

Create 8 D flip flops with high level active asynchronous reset. All DFF s shall be triggered by the rising edge of clk.

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output [7:0] q

);

always@(posedge clk or posedge areset)begin

if(areset)

q <= 8'b0;

else

q <= d;

end

endmodule

6. DFF with byte enable

Create 16 D triggers. Sometimes it is useful to modify only part of a set of triggers. The byte enable input controls whether each byte of the 16 registers should be written in this cycle. byteena[1] controls the high byte d[15:8], while byteena[0] controls the low byte d[7:0].

resetn is a synchronous, low-level active reset.

All DFF s shall be triggered by the rising edge of clk.

module top_module( input clk, input resetn, input [1:0] byteena, input [15:0] d, inpt [15:0] q); always@(posedge clk)begin if(~resetn)begin q <= 16'd0; end else if(byteena[0] || byteena[1]) begin if(byteena[1]) q[15:8] <= d[15:8]; else q[15:8] <= q[15:8]; if(byteena[0]) q[7:0] <= d[7:0]; else q[7:0] <= q[7:0]; end end endmodule

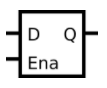

7. D Latch

module top_module( input d, input ena, output q); always@(*)begin if(ena)begin q = d; end end endmodule

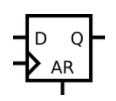

8. DFF

module top_module( input clk, input d, input ar, output q); always@(posedge clk or posedge ar)begin if(ar) begin q <= 1'd0; end else begin q <= d; end end endmodule

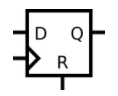

9. DFF

module top_module( input clk, input d, input r, input q); always@(posedge clk)begin if(r)begin q <= 1'b0; end else begin q <= d; end end endmodule

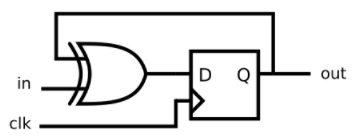

10. DFF+gate

module top_module( input clk, input in, output out); always@(posedge clk)begin out <= in ^ out; end endmodule

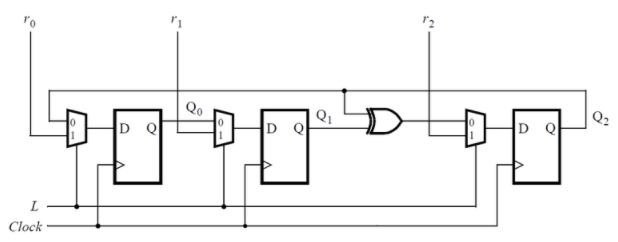

11. Mux and DFF

Suppose you want to implement layered Verilog code for this circuit, using three instances of a sub module with a trigger and multiplexer. Write a sub module called top for this sub module_ Verilog module of module (including a trigger and multiplexer)

module top_module( input clk, input L, input r_in, input q_in, output reg Q); always@(posedge clk)begin Q <= L?r_in:q_in; end endmodule

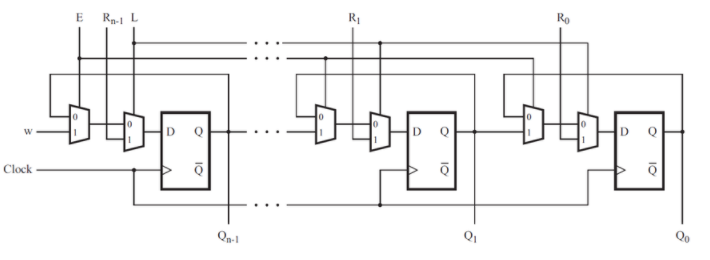

12. Mux and DFF

Write a Verilog module for one stage of the circuit, and the top-level module includes trigger and multiplexer

module top_module (

input clk,

input w, R, E, L,

output Q

);

wire temp1,temp2;

assign temp1 = E ? w:Q;

assign temp2 = L ? R:temp1;

always@(posedge clk)begin

Q <= temp2;

end

endmodule

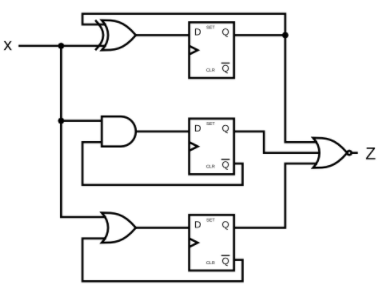

13.DFFs and gates

module top_module (

input clk,

input x,

output z

);

reg q1,q2,q3;

always@(posedge clk)begin

q1 <= x ^ q1;

q2 <= x &~ q2;

q3 <= x |~ q3;

end

assign z = ~(q1|q2|q3);

endmodule

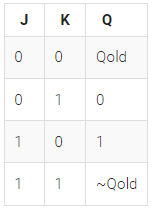

14.Create circuit from truth table

The K trigger has the following truth table. Only D flip flops and logic gates are used to implement JK flip flops. Note: Qold is the output of the D flip-flop before the rising edge of the clock.

module top_module (

input clk,

input j,

input k,

output Q);

always@(posedge clk)begin

case({j,k})

2'b00: Q <= Q;

2'b01: Q <= 0;

2'b10: Q <= 1;

2'b11: Q <= ~Q;

endcase

end

endmodule

15. Detect an edges

Characteristics of pulse edge: the levels on both sides have changed

If the falling edge is detected, it is that the high level changes to the low level.

If the rising edge is detected, the low level changes to high level.

If the edge of the pulse is detected, it only needs to do XOR operation on the incoming signals, that is, if the two levels are different, it is the edge.

module top_module (

input clk,

input [7:0] in,

output [7:0] pedge

);

reg [7:0] temp;

always @(posedge clk) begin

temp <= in;//temp is always one cycle later than in

pedge <= ~temp & in;

end

endmodule

16. Detect both edges

module top_module (

input clk,

input [7:0] in,

output [7:0] anyedge

);

reg [7:0] in_temp;

always @(posedge clk)begin

in_temp <= in;

anyedge <= in ^ in_temp;

end

endmodule

17.Edge capture register

For each bit in the 32-bit vector, when the input signal changes from 1 of one clock cycle to 0 of the next clock cycle, "capture" means that the output will remain 1 until it is reset (synchronous reset).

Each output bit behaves like an SR trigger: the output bit should be set (to 1) in the cycle after the 1 to 0 conversion occurs. When reset to high, the output bit should be reset at the positive clock edge (0). If the above two events occur at the same time, reset has priority.

In the last four cycles of the following example waveform, the "reset" event occurs one cycle earlier than the "set" event, so there is no conflict here.

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg [31:0] temp;

wire [31:0] capture;

always@(posedge clk)begin

temp <= in;

end

assign capture = ~in & temp;

always @(posedge clk)begin

if(reset)

out <= 32'b0;

else

begin

for (int i=0; i<32; i=i+1)

begin

if(capture[i] == 1'b1)

out[i] <= 1'b1;

end

end

end

endmodule

18.Dual-edge triggered flip-flop

Clock double edge trigger (the following code cannot be used and cannot be integrated)

~~always @(posedge clk or negedge clk)~~

module top_module (

input clk,

input d,

output q

);

reg q1,q2;

always@(posedge clk)begin

q1 <= d;

end

always@(negedge clk)begin

q2 <= d;

end

assign q = clk?q1:q2;

endmodule