Development environment: win7 64 bit + Ubuntu 16.04 64 bit

Development Board: tiny4412ADK + S700 + 4GB eMMC + 1G DDR3

Tool Chain: The arm-linux-gnueabihf - (gcc version 6.3.0) // lower version of the tool provided by the Friendly Arm does not compile the latest uboot

U-boot version to be transplanted: u-boot-2019-01

git Warehouse Address: https://github.com/songchong11/tiny4412-uboot-2019.git

1. transplantation

With the latest uboot-2019-01, it actually has good support for exynos 4412.

There are many types of boards / Samsung for our reference: origen, odroid, trats, trats2, etc. But only Origen supports configuring SPL, which is suitable for tiny4412, and the other three are not suitable for tiny4412. Taking odroid as an example, this configuration finally compiles a mirror u-boot-dtb.bin without spl. Combining with the start-up of exynos4412, even if the first 14k of u-boot-dtb.bin is forcibly cut out as BL2, the relative addresses of some functions called in board_init_f in BL2 code (as opposed to spl's). The starting address, 0x02023400) has exceeded 24KB, or even 16KB. We know that BL2 runs in iRAM and has an address space of up to 16KB, which can cause problems.

Now start transplanting:

Modify the top-level Makefile to specify the compiler and chip architecture as ARM

diff --git a/Makefile b/Makefile index 6aa0896..94906d1 100644 --- a/Makefile +++ b/Makefile @@ -243,7 +243,9 @@ export HOSTARCH HOSTOS ifeq ($(HOSTARCH),$(ARCH)) CROSS_COMPILE ?= endif - +ARCH = arm +CROSS_COMPILE = arm-linux-gnueabihf- KCONFIG_CONFIG ?= .config export KCONFIG_CONFIG @@ -906,8 +908,8 @@ cmd_pad_cat = $(cmd_objcopy) && $(append) || rm -f $@ cfg: u-boot.cfg

Copy exynos441-origen.dts file as exynos4412-tiny4412.dts, and modify Makefile

diff --git a/arch/arm/dts/Makefile b/arch/arm/dts/Makefile

index dda4e59..a71d08d 100644

--- a/arch/arm/dts/Makefile

+++ b/arch/arm/dts/Makefile

@@ -12,7 +12,8 @@ dtb-$(CONFIG_EXYNOS4) += exynos4210-origen.dtb \

exynos4210-universal_c210.dtb \

exynos4210-trats.dtb \

exynos4412-trats2.dtb \

- exynos4412-odroid.dtb

+ exynos4412-tiny4412.dtb

---------------------------------

Add exynos 4412-tiny4412.dts and modify it

diff --git a/arch/arm/dts/exynos4412-tiny4412.dts b/arch/arm/dts/exynos4412-tiny4412.dts

new file mode 100755

index 0000000..898a6a5

--- /dev/null

+++ b/arch/arm/dts/exynos4412-tiny4412.dts

@@ -0,0 +1,287 @@

+// SPDX-License-Identifier: GPL-2.0+

+/*

+ * Odroid-U3/X2 board device tree source

+ *

+ * Copyright (c) 2014 Samsung Electronics Co., Ltd.

+ * http://www.samsung.com

+ */

+

+/dts-v1/;

+#include "exynos4412.dtsi"

+

+/ {

+ model = "FriendlyARM TINY4412 board based on Exynos4412";

+ compatible = "friendlyarm,tiny4412", "samsung,exynos4412", "samsung,exynos4";

+

+ chosen {

+ stdout-path = "serial0";

+ bootargs ="";

+ };

+ aliases {

+ serial0 = "/serial@13800000";

+ console = "/serial@13800000";

+ //mmc0 = &mshc_0;

+ //mmc1 = &sdhci2;

+ mmc0 = "/sdhci@12530000";

+ mmc1 = "/dwmmc@12550000";

+ };

+

+ serial0:serial@13810000 {

+ status = "okay";

+ };

+

+ ehci@12580000 {

+ compatible = "samsung,exynos-ehci";

+ reg = <0x12580000 0x100>;

+ #address-cells = <1>;

+ #size-cells = <1>;

+ phy {

+ compatible = "samsung,exynos-usb-phy";

+ reg = <0x125B0000 0x100>;

+ };

+ };

+ sdhci@12510000 {

+ compatible = "samsung,exynos4412-sdhci";

+ status = "disabled";

+ };

+

+ sdhci@12520000 {

+ compatible = "samsung,exynos4412-sdhci";

+ status = "disabled";

+ };

+

+ sdhci@12530000 {

+ compatible = "samsung,exynos4412-sdhci";

+ samsung,bus-width = <4>;

+ samsung,timing = <1 2 3>;

+ cd-gpios = <&gpk2 2 0>;

+ };

+

+ sdhci@12540000 {

+ compatible = "samsung,exynos4412-sdhci";

+ status = "disabled";

+ };

+ dwmmc@12550000 {

+ samsung,bus-width = <8>;

+ samsung,timing = <2 1 0>;

+ samsung,removable = <0>;

+ fifoth_val = <0x203f0040>;

+ bus_hz = <400000000>;

+ div = <0x3>;

+ index = <4>;

+ };

+ emmc-reset {

+ compatible = "samsung,emmc-reset";

+ reset-gpio = <&gpk1 2 0>;

+ };

+};

+

+&sdhci2 {

+ samsung,bus-width = <4>;

+ samsung,timing = <1 2 3>;

+ cd-gpios = <&gpk2 2 0>;

+ status = "okay";

+};

+

+&mshc_0 {

+ samsung,bus-width = <8>;

+ samsung,timing = <2 1 0>;

+ samsung,removable = <0>;

+ fifoth_val = <0x203f0040>;

+ bus_hz = <400000000>;

+ div = <0x3>;

+ index = <4>;

+ status = "okay";

+};Add tiny4412 machine ID

diff --git a/arch/arm/include/asm/mach-types.h b/arch/arm/include/asm/mach-types.h index 9f82efe..e8caba0 100644 --- a/arch/arm/include/asm/mach-types.h +++ b/arch/arm/include/asm/mach-types.h @@ -3403,6 +3403,7 @@ #define MACH_TYPE_MONCH 3453 #define MACH_TYPE_CURACAO 3454 #define MACH_TYPE_ORIGEN 3455 +#define MACH_TYPE_TINY4412 4608 #define MACH_TYPE_EPC10 3456 #define MACH_TYPE_SGH_I740 3457 #define MACH_TYPE_TUNA 3458

Modify arch/arm/mach-exynos/Kconfig file to see our changes when making menuconfig is executed

diff --git a/arch/arm/mach-exynos/Kconfig b/arch/arm/mach-exynos/Kconfig

old mode 100644

new mode 100755

index ed04369..1735381

--- a/arch/arm/mach-exynos/Kconfig

+++ b/arch/arm/mach-exynos/Kconfig

@@ -59,6 +59,10 @@ config TARGET_S5PC210_UNIVERSAL

config TARGET_ORIGEN

bool "Exynos4412 Origen board"

select SUPPORT_SPL

+

+config TARGET_TINY4412

+ bool "Exynos4412 Tiny4412 board"

+ select SUPPORT_SPL

config TARGET_TRATS2

bool "Exynos4412 Trat2 board"

@@ -156,6 +160,7 @@ source "board/samsung/smdkv310/Kconfig"

source "board/samsung/trats/Kconfig"

source "board/samsung/universal_c210/Kconfig"

source "board/samsung/origen/Kconfig"

+source "board/samsung/tiny4412/Kconfig"

source "board/samsung/trats2/Kconfig"

source "board/samsung/odroid/Kconfig"

source "board/samsung/arndale/Kconfig"Modify/arch/arm/mach-exynos/Makefile

diff --git a/arch/arm/mach-exynos/Makefile b/arch/arm/mach-exynos/Makefile index e895c13..8597e08 100644 --- a/arch/arm/mach-exynos/Makefile +++ b/arch/arm/mach-exynos/Makefile @@ -12,7 +12,10 @@ obj-$(CONFIG_EXYNOS5420) += sec_boot.o ifdef CONFIG_SPL_BUILD obj-$(CONFIG_EXYNOS5) += clock_init_exynos5.o obj-$(CONFIG_EXYNOS5) += dmc_common.o dmc_init_ddr3.o -obj-$(CONFIG_EXYNOS4210)+= dmc_init_exynos4.o clock_init_exynos4.o +#obj-$(CONFIG_EXYNOS4210)+= dmc_init_exynos4.o clock_init_exynos4.o +ifneq (,$(filter y, $(CONFIG_EXYNOS4210)$(CONFIG_TINY4412))) +obj-y += dmc_init_exynos4.o clock_init_exynos4.o obj-y += spl_boot.o tzpc.o obj-y += lowlevel_init.o endif +endif

Modify the clock register to initialize the clock

diff --git a/arch/arm/mach-exynos/clock_init_exynos4.c b/arch/arm/mach-exynos/clock_init_exynos4.c

old mode 100644

new mode 100755

index 584e4ba..fda1837

--- a/arch/arm/mach-exynos/clock_init_exynos4.c

+++ b/arch/arm/mach-exynos/clock_init_exynos4.c

@@ -38,42 +38,39 @@

*/

void system_clock_init(void)

{

- struct exynos4_clock *clk =

- (struct exynos4_clock *)samsung_get_base_clock();

+ struct exynos4x12_clock *clk =

+ (struct exynos4x12_clock *)samsung_get_base_clock();

- writel(CLK_SRC_CPU_VAL, &clk->src_cpu);

+ /* APLL= 1400 MHz MPLL=800 MHz */

+

+ writel(0x01000001, &clk->src_cpu);

sdelay(0x10000);

- writel(CLK_SRC_TOP0_VAL, &clk->src_top0);

- writel(CLK_SRC_TOP1_VAL, &clk->src_top1);

- writel(CLK_SRC_DMC_VAL, &clk->src_dmc);

- writel(CLK_SRC_LEFTBUS_VAL, &clk->src_leftbus);

- writel(CLK_SRC_RIGHTBUS_VAL, &clk->src_rightbus);

+ writel(0x10, &clk->src_leftbus);

+ writel(0x10, &clk->src_rightbus);

+ writel(0x110, &clk->src_top0);

+ writel(0x1111000, &clk->src_top1);

+ writel(0x00011000, &clk->src_dmc);

writel(CLK_SRC_FSYS_VAL, &clk->src_fsys);

writel(CLK_SRC_PERIL0_VAL, &clk->src_peril0);

writel(CLK_SRC_CAM_VAL, &clk->src_cam);

writel(CLK_SRC_MFC_VAL, &clk->src_mfc);

writel(CLK_SRC_G3D_VAL, &clk->src_g3d);

- writel(CLK_SRC_LCD0_VAL, &clk->src_lcd0);

sdelay(0x10000);

- writel(CLK_DIV_CPU0_VAL, &clk->div_cpu0);

- writel(CLK_DIV_CPU1_VAL, &clk->div_cpu1);

- writel(CLK_DIV_DMC0_VAL, &clk->div_dmc0);

- writel(CLK_DIV_DMC1_VAL, &clk->div_dmc1);

- writel(CLK_DIV_LEFTBUS_VAL, &clk->div_leftbus);

- writel(CLK_DIV_RIGHTBUS_VAL, &clk->div_rightbus);

- writel(CLK_DIV_TOP_VAL, &clk->div_top);

+ writel(0x1160730, &clk->div_cpu0);

+ writel(0x506, &clk->div_cpu1);

+ writel(0x111113, &clk->div_dmc0);

+ writel(0x1011713, &clk->div_dmc1);

writel(CLK_DIV_FSYS1_VAL, &clk->div_fsys1);

- writel(CLK_DIV_FSYS2_VAL, &clk->div_fsys2);

+ writel(0x4070047, &clk->div_fsys2);

writel(CLK_DIV_FSYS3_VAL, &clk->div_fsys3);

writel(CLK_DIV_PERIL0_VAL, &clk->div_peril0);

writel(CLK_DIV_CAM_VAL, &clk->div_cam);

writel(CLK_DIV_MFC_VAL, &clk->div_mfc);

writel(CLK_DIV_G3D_VAL, &clk->div_g3d);

- writel(CLK_DIV_LCD0_VAL, &clk->div_lcd0);

/* Set PLL locktime */

writel(PLL_LOCKTIME, &clk->apll_lock);

@@ -81,10 +78,10 @@ void system_clock_init(void)

writel(PLL_LOCKTIME, &clk->epll_lock);

writel(PLL_LOCKTIME, &clk->vpll_lock);

- writel(APLL_CON1_VAL, &clk->apll_con1);

- writel(APLL_CON0_VAL, &clk->apll_con0);

- writel(MPLL_CON1_VAL, &clk->mpll_con1);

- writel(MPLL_CON0_VAL, &clk->mpll_con0);

+ writel(0x803800, &clk->apll_con1);

+ writel(0x80af0300, &clk->apll_con0);

+ writel(0x803800, &clk->mpll_con1);

+ writel(0x80640300, &clk->mpll_con0);

writel(EPLL_CON1_VAL, &clk->epll_con1);

writel(EPLL_CON0_VAL, &clk->epll_con0);

writel(VPLL_CON1_VAL, &clk->vpll_con1);

(END)Initialization of Modified drm

diff --git a/arch/arm/mach-exynos/dmc_init_exynos4.c b/arch/arm/mach-exynos/dmc_init_exynos4.c

old mode 100644

new mode 100755

index ecddc72..69e9fd6

--- a/arch/arm/mach-exynos/dmc_init_exynos4.c

+++ b/arch/arm/mach-exynos/dmc_init_exynos4.c

@@ -32,19 +32,19 @@ struct mem_timings mem = {

.direct_cmd_msr = {

DIRECT_CMD1, DIRECT_CMD2, DIRECT_CMD3, DIRECT_CMD4

},

- .timingref = TIMINGREF_VAL,

- .timingrow = TIMINGROW_VAL,

- .timingdata = TIMINGDATA_VAL,

- .timingpower = TIMINGPOWER_VAL,

- .zqcontrol = ZQ_CONTROL_VAL,

- .control0 = CONTROL0_VAL,

- .control1 = CONTROL1_VAL,

- .control2 = CONTROL2_VAL,

- .concontrol = CONCONTROL_VAL,

- .prechconfig = PRECHCONFIG,

- .memcontrol = MEMCONTROL_VAL,

- .memconfig0 = MEMCONFIG0_VAL,

- .memconfig1 = MEMCONFIG1_VAL,

+ .timingref = 0x000000bb,//TIMINGREF_VAL,

+ .timingrow = 0x7a46654f,//TIMINGROW_VAL,

+ .timingdata = 0x46400506,//TIMINGDATA_VAL,

+ .timingpower = 0x52000a3c,//TIMINGPOWER_VAL,

+ .zqcontrol = 0xe3854c03,//ZQ_CONTROL_VAL,

+ .control0 = 0x7110100b,//CONTROL0_VAL,

+ .control1 = 0xe0000086,//CONTROL1_VAL,

+ .control2 = 0x00000000,//CONTROL2_VAL,

+ .concontrol = 0x0fff333a,//CONCONTROL_VAL,

+ .prechconfig = 0xff000000,//PRECHCONFIG,

+ .memcontrol = 0x00302640,//MEMCONTROL_VAL,

+ .memconfig0 = 0x40c01333,//MEMCONFIG0_VAL,

+ .memconfig1 = 0x80e01323,//MEMCONFIG1_VAL,

.dll_resync = FORCE_DLL_RESYNC,

.dll_on = DLL_CONTROL_ON,

};

@@ -124,6 +124,8 @@ static void dmc_init(struct exynos4_dmc *dmc)

writel(mem.memconfig0, &dmc->memconfig0);

writel(mem.memconfig1, &dmc->memconfig1);

+ writel(0x8000001F, &dmc->ivcontrol);

+

/* Config Precharge Policy */

writel(mem.prechconfig, &dmc->prechconfig);

/*Modify some configuration of dmc

diff --git a/arch/arm/mach-exynos/exynos4_setup.h b/arch/arm/mach-exynos/exynos4_setup.h

old mode 100644

new mode 100755

index 38735f0..4fb5444

--- a/arch/arm/mach-exynos/exynos4_setup.h

+++ b/arch/arm/mach-exynos/exynos4_setup.h

@@ -5,8 +5,11 @@

* Copyright (C) 2011 Samsung Electronics

*/

-#ifndef _ORIGEN_SETUP_H

-#define _ORIGEN_SETUP_H

+//#ifndef _ORIGEN_SETUP_H

+//#define _ORIGEN_SETUP_H

+

+#ifndef _TINY4412_SETUP_H

+#define _TINY4412_SETUP_H

#include <config.h>

#include <asm/arch/cpu.h>

@@ -433,7 +436,7 @@ struct mem_timings {

#define ABP_SFR_SLV1_SINGLE_ADDRMAP_START_OFFSET 0x828

#define ABP_SFR_SLV1_SINGLE_ADDRMAP_END_OFFSET 0x830

-#ifdef CONFIG_ORIGEN

+#if (defined CONFIG_ORIGEN) || (defined CONFIG_TINY4412)

/* Interleave: 2Bit, Interleave_bit1: 0x15, Interleave_bit0: 0x7 */

#define APB_SFR_INTERLEAVE_CONF_VAL 0x20001507

#define APB_SFR_ARBRITATION_CONF_VAL 0x00000001

@@ -505,7 +508,7 @@ struct mem_timings {

#define ADD_LAT_PALL (1 << 6)

#define MEM_TYPE_DDR3 (0x6 << 8)

#define MEM_WIDTH_32 (0x2 << 12)

-#define NUM_CHIP_2 (1 << 16)

+#define NUM_CHIP_2 (0 << 16)

#define BL_8 (0x3 << 20)

#define MEMCONTROL_VAL (CLK_STOP_DISABLE | DPWRDN_DISABLE\

| DPWRDN_TYPE | TP_DISABLE | DSREF_DIABLE\

@@ -514,16 +517,16 @@ struct mem_timings {

#define CHIP_BANK_8 (0x3 << 0)

-#define CHIP_ROW_14 (0x2 << 4)

+#define CHIP_ROW_14 (0x3 << 4)

#define CHIP_COL_10 (0x3 << 8)

#define CHIP_MAP_INTERLEAVED (1 << 12)

-#define CHIP_MASK (0xe0 << 16)

+#define CHIP_MASK (0xC0 << 16)

#ifdef CONFIG_MIU_LINEAR

#define CHIP0_BASE (0x40 << 24)

#define CHIP1_BASE (0x60 << 24)

#else

-#define CHIP0_BASE (0x20 << 24)

-#define CHIP1_BASE (0x40 << 24)

+#define CHIP0_BASE (0x40 << 24)

+#define CHIP1_BASE (0x80 << 24)

#endif

#define MEMCONFIG0_VAL (CHIP_BANK_8 | CHIP_ROW_14 | CHIP_COL_10\

| CHIP_MAP_INTERLEAVED | CHIP_MASK | CHIP0_BASE)

@@ -555,7 +558,7 @@ struct mem_timings {

#define CONTROL2_VAL 0x00000000

-#ifdef CONFIG_ORIGEN

+#if (defined CONFIG_ORIGEN) || (defined CONFIG_TINY4412)

#define TIMINGREF_VAL 0x000000BB

#define TIMINGROW_VAL 0x4046654f

#define TIMINGDATA_VAL 0x46400506

(END)Initialize Serial Port 0 as Print Output Port

diff --git a/arch/arm/mach-exynos/lowlevel_init.c b/arch/arm/mach-exynos/lowlevel_init.c

index 1e090fd..8cae6b9 100644

--- a/arch/arm/mach-exynos/lowlevel_init.c

+++ b/arch/arm/mach-exynos/lowlevel_init.c

@@ -216,14 +216,17 @@ int do_lowlevel_init(void)

if (actions & DO_CLOCKS) {

system_clock_init();

#ifdef CONFIG_DEBUG_UART

-#if (defined(CONFIG_SPL_BUILD) && defined(CONFIG_SPL_SERIAL_SUPPORT)) || \

+//#if (defined(CONFIG_SPL_BUILD) && defined(CONFIG_SPL_SERIAL_SUPPORT)) || \

!defined(CONFIG_SPL_BUILD)

- exynos_pinmux_config(PERIPH_ID_UART3, PINMUX_FLAG_NONE);

+ exynos_pinmux_config(PERIPH_ID_UART0, PINMUX_FLAG_NONE);

debug_uart_init();

-#endif

+ printascii("UART OK \n\r");

+//#endif

#endif

mem_ctrl_init(actions & DO_MEM_RESET);

+ printascii("mem ctrl init ok \n\r");

tzpc_init();

+ printascii("tzpc_init ok \n\r");

}Modify trust zone, otherwise some buses will not work

diff --git a/arch/arm/mach-exynos/tzpc.c b/arch/arm/mach-exynos/tzpc.c

old mode 100644

new mode 100755

index abe8e7f..63605d5

--- a/arch/arm/mach-exynos/tzpc.c

+++ b/arch/arm/mach-exynos/tzpc.c

@@ -17,10 +17,7 @@ void tzpc_init(void)

start = samsung_get_base_tzpc();

- if (cpu_is_exynos5())

- end = start + ((EXYNOS5_NR_TZPC_BANKS - 1) * TZPC_BASE_OFFSET);

- else if (cpu_is_exynos4())

- end = start + ((EXYNOS4_NR_TZPC_BANKS - 1) * TZPC_BASE_OFFSET);

+ end = start + ((EXYNOS4_NR_TZPC_BANKS - 1) * TZPC_BASE_OFFSET);

for (addr = start; addr <= end; addr += TZPC_BASE_OFFSET) {

tzpc = (struct exynos_tzpc *)addr;

@@ -30,11 +27,7 @@ void tzpc_init(void)

writel(DECPROTXSET, &tzpc->decprot0set);

writel(DECPROTXSET, &tzpc->decprot1set);

-

- if (cpu_is_exynos5() && (addr == end))

- break;

-

- writel(DECPROTXSET, &tzpc->decprot2set);

+ writel(0xbd, &tzpc->decprot2set);

writel(DECPROTXSET, &tzpc->decprot3set);

}

}Simulate the board/samsung/origen folder to add the board/samsung/tiny4412 folder and modify the file name inside.

board/samsung/tiny4412/Kconfig

board/samsung/tiny4412/MAINTAINERS

board/samsung/tiny4412/Makefile

board/samsung/tiny4412/tiny4412.c

board/samsung/tiny4412/tools/mktiny4412spl.c

Modify Kconfig file

diff --git a/board/samsung/tiny4412/Kconfig b/board/samsung/tiny4412/Kconfig new file mode 100644 index 0000000..04658fe --- /dev/null +++ b/board/samsung/tiny4412/Kconfig @@ -0,0 +1,16 @@ +if TARGET_TINY4412 + +config TINY4412 + default y + bool "For CONFIG_TINY4412" + +config SYS_BOARD + default "tiny4412" + +config SYS_VENDOR + default "samsung" + +config SYS_CONFIG_NAME + default "tiny4412" + +endif

Add the following files

diff --git a/board/samsung/tiny4412/MAINTAINERS b/board/samsung/tiny4412/MAINTAINERS new file mode 100755 index 0000000..4f2fd06 --- /dev/null +++ b/board/samsung/tiny4412/MAINTAINERS @@ -0,0 +1,6 @@ +TINY4412 BOARD +M: Song Chong <1972433980@qq.com> +S: Maintained +F: board/samsung/tiny4412/ +F: include/configs/tiny4412.h +F: configs/tiny4412_defconfig

diff --git a/board/samsung/tiny4412/tiny4412.c b/board/samsung/tiny4412/tiny4412.c

new file mode 100755

index 0000000..eca942a

--- /dev/null

+++ b/board/samsung/tiny4412/tiny4412.c

@@ -0,0 +1,37 @@

+// SPDX-License-Identifier: GPL-2.0+

+/*

+ * Copyright (C) 2011 Samsung Electronics

+ */

+

+#include <common.h>

+#include <asm/io.h>

+#include <asm/gpio.h>

+#include <asm/arch/cpu.h>

+#include <asm/arch/mmc.h>

+#include <asm/arch/periph.h>

+#include <asm/arch/pinmux.h>

+#include <usb.h>

+

+DECLARE_GLOBAL_DATA_PTR;

+

+u32 get_board_rev(void)

+{

+ return 0;

+}

+

+int exynos_init(void)

+{

+ return 0;

+}

+

+int board_usb_init(int index, enum usb_init_type init)

+{

+ return 0;

+}

+

+#ifdef CONFIG_BOARD_EARLY_INIT_F

+int exynos_early_init_f(void)

+{

+ return 0;

+}

+#endifdiff --git a/board/samsung/tiny4412/tools/mktiny4412spl.c b/board/samsung/tiny4412/tools/mktiny4412spl.c

new file mode 100644

index 0000000..f4be867

--- /dev/null

+++ b/board/samsung/tiny4412/tools/mktiny4412spl.c

@@ -0,0 +1,109 @@

+// SPDX-License-Identifier: GPL-2.0+

+/*

+ * Copyright (C) 2011 Samsung Electronics

+ */

+

+#include <stdio.h>

+#include <stdlib.h>

+#include <unistd.h>

+#include <fcntl.h>

+#include <errno.h>

+#include <string.h>

+#include <sys/stat.h>

+

+#define BUFSIZE (16*1024)

+#define IMG_SIZE (16*1024)

+#define SPL_HEADER_SIZE 16

+#define FILE_PERM (S_IRUSR | S_IWUSR | S_IRGRP \

+ | S_IWGRP | S_IROTH | S_IWOTH)

+#define SPL_HEADER "S5PC210 HEADER "

+/*

+* Requirement:

+* IROM code reads first 14K bytes from boot device.

+* It then calculates the checksum of 14K-4 bytes and compare with data at

+* 14K-4 offset.

+*

+* This function takes two filenames:

+* IN "u-boot-spl.bin" and

+* OUT "$(BOARD)-spl.bin as filenames.

+* It reads the "u-boot-spl.bin" in 16K buffer.

+* It calculates checksum of 14K-4 Bytes and stores at 14K-4 offset in buffer.

+* It writes the buffer to "$(BOARD)-spl.bin" file.

+*/

+

+int main(int argc, char **argv)

+{

+ int i, len;

+ unsigned char buffer[BUFSIZE] = {0};

+ int ifd, ofd;

+ unsigned int checksum = 0, count;

+

+ if (argc != 3) {

+ printf(" %d Wrong number of arguments\n", argc);

+ exit(EXIT_FAILURE);

+ }

+

+ ifd = open(argv[1], O_RDONLY);

+ if (ifd < 0) {

+ fprintf(stderr, "%s: Can't open %s: %s\n",

+ argv[0], argv[1], strerror(errno));

+ exit(EXIT_FAILURE);

+ }

+

+ ofd = open(argv[2], O_WRONLY | O_CREAT | O_TRUNC, FILE_PERM);

+ if (ofd < 0) {

+ fprintf(stderr, "%s: Can't open %s: %s\n",

+ argv[0], argv[2], strerror(errno));

+ if (ifd)

+ close(ifd);

+ exit(EXIT_FAILURE);

+ }

+

+ len = lseek(ifd, 0, SEEK_END);

+ lseek(ifd, 0, SEEK_SET);

+

+ memcpy(&buffer[0], SPL_HEADER, SPL_HEADER_SIZE);

+

+ count = (len < (IMG_SIZE - SPL_HEADER_SIZE))

+ ? len : (IMG_SIZE - SPL_HEADER_SIZE);

+

+ if (read(ifd, buffer + SPL_HEADER_SIZE, count) != count) {

+ fprintf(stderr, "%s: Can't read %s: %s\n",

+ argv[0], argv[1], strerror(errno));

+

+ if (ifd)

+ close(ifd);

+ if (ofd)

+ close(ofd);

+

+ exit(EXIT_FAILURE);

+ }

+

+ for (i = 0; i < IMG_SIZE - SPL_HEADER_SIZE; i++)

+ checksum += buffer[i+16];

+

+ *(unsigned long *)buffer ^= 0x1f;

+ *(unsigned long *)(buffer+4) ^= checksum;

+

+ for (i = 1; i < SPL_HEADER_SIZE; i++)

+ buffer[i] ^= buffer[i-1];

+

+ if (write(ofd, buffer, BUFSIZE) != BUFSIZE) {

+ fprintf(stderr, "%s: Can't write %s: %s\n",

+ argv[0], argv[2], strerror(errno));

+

+ if (ifd)

+ close(ifd);

+ if (ofd)

+ close(ofd);

+

+ exit(EXIT_FAILURE);

+ }

+

+ if (ifd)

+ close(ifd);

+ if (ofd)

+ close(ofd);

+

+ return EXIT_SUCCESS;

+}Add a print to see if uboot runs

diff --git a/common/board_f.c b/common/board_f.c

index 149a722..f0fbf13 100644

--- a/common/board_f.c

+++ b/common/board_f.c

@@ -43,7 +43,7 @@

#include <asm/sections.h>

#include <dm/root.h>

#include <linux/errno.h>

-

+#include <debug_uart.h>

/*

* Pointer to initial global data area

*

@@ -985,6 +985,7 @@ static const init_fnc_t init_sequence_f[] = {

void board_init_f(ulong boot_flags)

{

+ printascii("uboot runnig.\r\n");

gd->flags = boot_flags;

gd->have_console = 0;Add configuration file tiny4412_defonfig

diff --git a/configs/tiny4412_defconfig b/configs/tiny4412_defconfig new file mode 100755 index 0000000..06b35fb --- /dev/null +++ b/configs/tiny4412_defconfig @@ -0,0 +1,49 @@ +CONFIG_ARM=y +CONFIG_ARCH_EXYNOS=y +CONFIG_TARGET_TINY4412=y +CONFIG_SYS_TEXT_BASE=0x43E00000 +CONFIG_ARCH_EXYNOS4=y +#CONFIG_TARGET_ORIGEN=y +CONFIG_SPL=y +CONFIG_IDENT_STRING=" for TINY4412" +CONFIG_DISTRO_DEFAULTS=y +# CONFIG_USE_BOOTCOMMAND is not set +CONFIG_SYS_CONSOLE_IS_IN_ENV=y +CONFIG_SYS_CONSOLE_INFO_QUIET=y +# CONFIG_SPL_FRAMEWORK is not set +CONFIG_SYS_PROMPT="TINY4412 # " +# CONFIG_CMD_XIMG is not set +CONFIG_CMD_THOR_DOWNLOAD=y +CONFIG_CMD_DFU=y +CONFIG_CMD_GPT=y +CONFIG_CMD_MMC=y +CONFIG_CMD_BOOTZ=y +CONFIG_CMD_MII=y +CONFIG_CMD_USB_MASS_STORAGE=y +# CONFIG_CMD_NET is not set +CONFIG_CMD_CACHE=y +CONFIG_CMD_EXT2=y +CONFIG_CMD_EXT4=y +CONFIG_CMD_EXT4_WRITE=y +CONFIG_CMD_FAT=y +CONFIG_CMD_FS_GENERIC=y +# CONFIG_CMD_MISC is not set +CONFIG_CMD_EXT4_WRITE=y +CONFIG_OF_CONTROL=y +CONFIG_DEFAULT_DEVICE_TREE="exynos4412-tiny4412" +CONFIG_DFU_MMC=y +CONFIG_DM_MMC=y +CONFIG_MMC_DW=y +CONFIG_MMC_SDHCI=y +CONFIG_MMC_SDHCI_SDMA=y +CONFIG_MMC_SDHCI_S5P=y +CONFIG_USB=y +CONFIG_DM_USB=y +CONFIG_USB_GADGET=y +CONFIG_USB_GADGET_MANUFACTURER="Samsung" +CONFIG_USB_GADGET_VENDOR_NUM=0x04e8 +CONFIG_USB_GADGET_PRODUCT_NUM=0x6601 +CONFIG_USB_GADGET_DWC2_OTG=y +CONFIG_USB_GADGET_DOWNLOAD=y +CONFIG_USB_FUNCTION_THOR=y +# CONFIG_REGEX is not set

Modify the serial initialization register

diff --git a/drivers/serial/serial_s5p.c b/drivers/serial/serial_s5p.c

index e3160cf..2de62f0 100644

--- a/drivers/serial/serial_s5p.c

+++ b/drivers/serial/serial_s5p.c

@@ -62,12 +62,12 @@ static const int udivslot[] = {

static void __maybe_unused s5p_serial_init(struct s5p_uart *uart)

{

/* enable FIFOs, auto clear Rx FIFO */

- writel(0x3, &uart->ufcon);

+ writel(0x11, &uart->ufcon);

writel(0, &uart->umcon);

/* 8N1 */

writel(0x3, &uart->ulcon);

/* No interrupts, no DMA, pure polling */

- writel(0x245, &uart->ucon);

+ writel(0x3c5, &uart->ucon);

}Add include/configs/tiny4412.h

diff --git a/include/configs/tiny4412.h b/include/configs/tiny4412.h

new file mode 100755

index 0000000..bc67d97

--- /dev/null

+++ b/include/configs/tiny4412.h

@@ -0,0 +1,134 @@

+/*

+ * Copyright (C) 2011 Samsung Electronics

+ *

+ * Configuration settings for the SAMSUNG TINY4412 (EXYNOS4412) board.

+ *

+ * SPDX-License-Identifier: GPL-2.0+

+ */

+

+#ifndef __CONFIG_TINY4412_H

+#define __CONFIG_TINY4412_H

+

+#include <configs/exynos4-common.h>

+

+/* High Level Configuration Options */

+#define CONFIG_TINY4412 1

+

+#define CONFIG_SPL_SERIAL_SUPPORT

+#define CONFIG_SPL_GPIO_SUPPORT

+#define CONFIG_DEBUG_UART

+#define CONFIG_DEBUG_UART_S5P

+#define CONFIG_DEBUG_UART_BASE 0x13800000 /* UART0 base address */

+#define CONFIG_DEBUG_UART_CLOCK (100000000) /* SCLK_UART0 is 100MHz */

+

+#define CONFIG_SYS_DCACHE_OFF 1

+

+/* ORIGEN has 4 bank of DRAM */

+#define CONFIG_NR_DRAM_BANKS 4

+#define CONFIG_SYS_SDRAM_BASE 0x40000000

+#define PHYS_SDRAM_1 CONFIG_SYS_SDRAM_BASE

+#define SDRAM_BANK_SIZE (256 << 20) /* 256 MB */

+

+/* memtest works on */

+#define CONFIG_SYS_MEMTEST_START CONFIG_SYS_SDRAM_BASE

+#define CONFIG_SYS_MEMTEST_END (CONFIG_SYS_SDRAM_BASE + 0x6000000)

+#define CONFIG_SYS_LOAD_ADDR (CONFIG_SYS_SDRAM_BASE + 0x3E00000)

+

+#define CONFIG_MACH_TYPE MACH_TYPE_TINY4412

+

+/* select serial console configuration */

+#define CONFIG_SERIAL2

+#define CONFIG_BAUDRATE 115200

+

+/* Console configuration */

+

+#define CONFIG_DEFAULT_CONSOLE "console=ttySAC0,115200n8\0"

+

+#define CONFIG_SYS_MEM_TOP_HIDE (1 << 20) /* ram console */

+

+#define CONFIG_SYS_MONITOR_BASE 0x00000000

+

+/* Power Down Modes */

+#define S5P_CHECK_SLEEP 0x00000BAD

+#define S5P_CHECK_DIDLE 0xBAD00000

+#define S5P_CHECK_LPA 0xABAD0000

+

+/* MMC SPL */

+#define COPY_BL2_FNPTR_ADDR 0x02020030

+/* Because bl1 will copy bl2(spl) to iram address 0x02023400 */

+#define CONFIG_SPL_TEXT_BASE 0x02023400

+

+#define CONFIG_EXTRA_ENV_SETTINGS \

+ "loadaddr=0x40007000\0" \

+ "rdaddr=0x48000000\0" \

+ "dtaddr=0x42000000\0" \

+ "kerneladdr=0x40007000\0" \

+ "ramdiskaddr=0x48000000\0" \

+ "dtbaddr=0x42000000\0" \

+ "console=ttySAC0,115200n8\0" \

+ "mmcdev=0\0" \

+ "bootenv=uEnv.txt\0" \

+ "loadbootenv=load mmc ${mmcdev} ${loadaddr} ${bootenv}\0" \

+ "importbootenv=echo Importing environment from mmc ...; " \

+ "env import -t $loadaddr $filesize\0" \

+ "loadbootscript=load mmc ${mmcdev} ${loadaddr} boot.scr\0" \

+ "bootscript=echo Running bootscript from mmc${mmcdev} ...; " \

+ "source ${loadaddr}\0"

+#define CONFIG_BOOTCOMMAND \

+ "if mmc rescan; then " \

+ "echo SD/MMC found on device ${mmcdev};" \

+ "if run loadbootenv; then " \

+ "echo Loaded environment from ${bootenv};" \

+ "run importbootenv;" \

+ "fi;" \

+ "if test -n $uenvcmd; then " \

+ "echo Running uenvcmd ...;" \

+ "run uenvcmd;" \

+ "fi;" \

+ "if run loadbootscript; then " \

+ "run bootscript; " \

+ "fi; " \

+ "fi;" \

+ "load mmc ${mmcdev} ${loadaddr} uImage;" \

+ "load mmc ${mmcdev} ${rdaddr} ramdisk.img;"\

+ "load mmc ${mmcdev} ${dtaddr} exynos4412-tiny4412.dtb; bootm ${loadaddr} "

+

+#define CONFIG_IDENT_STRING " for TINY4412"

+

+#define CONFIG_CLK_1000_400_200

+

+/* MIU (Memory Interleaving Unit) */

+#define CONFIG_MIU_2BIT_21_7_INTERLEAVED

+

+/*

+ * SD MMC layout:

+ * +------------+------------------------------------------------------------+

+ * | |

+ * | | | | | |

+ * | 512B | 8K(bl1) | 16k(bl2) | 16k(ENV) | 512k(u-boot) |

+ * | | | | | |

+ * | |

+ * +------------+------------------------------------------------------------+

+ *

+ */

+

+#define CONFIG_SYS_MMC_ENV_DEV 0

+#define CONFIG_ENV_SIZE (16 << 10) /* 16 KB */

+#define RESERVE_BLOCK_SIZE (512)

+#define BL1_SIZE (8 << 10) /*16 K reserved for BL1*/

+#define BL2_SIZE (16 << 10) /*16 k reserved for BL2*/

+#define CONFIG_ENV_OFFSET (RESERVE_BLOCK_SIZE + BL1_SIZE + BL2_SIZE)

+

+#define CONFIG_SPL_LDSCRIPT "board/samsung/common/exynos-uboot-spl.lds"

+#define CONFIG_SPL_MAX_FOOTPRINT (14 * 1024)

+

+#define CONFIG_SYS_INIT_SP_ADDR 0x02040000

+

+/* U-Boot copy size from boot Media to DRAM.*/

+#define COPY_BL2_SIZE 0x80000

+#define BL2_START_OFFSET ((CONFIG_ENV_OFFSET + CONFIG_ENV_SIZE)/512)

+#define BL2_SIZE_BLOC_COUNT (COPY_BL2_SIZE/512)

+

+/* #define UBOOT_DEBUG_20151226 */

+

+#endif /* __CONFIG_H */Add an automated compiler script to facilitate compilation

diff --git a/make.sh b/make.sh new file mode 100755 index 0000000..579407d --- /dev/null +++ b/make.sh @@ -0,0 +1,2 @@ +make ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- +make tiny4412_defconfig && make

Add an automatic burning SD card, make the script to start the card. Among them, / dev/sdb is recognized as sdb1 by the linux machine whose SD card is compiled by uboot.

Different machines may recognize different things, some of them are / dev/sdc, etc., which can be viewed through the df command.

diff --git a/run.sh b/run.sh new file mode 100755 index 0000000..925b7ad --- /dev/null +++ b/run.sh @@ -0,0 +1,7 @@ +echo -e "\033[45m start fusing \033[0m" + +cd sd_fuse/tiny4412/ +./sd_fusing.sh /dev/sdb +cd ../.. + +echo -e "\033[45m fusing over \033[0m"

In the uboot given by Friendly Arm, there is a sd_fuse folder that needs to be copied. I put it in the root directory of uboot.

V310-EVT1-mkbl2.c is used to produce mkbl2 tools, there is a place to be modified.

diff --git a/sd_fuse/V310-EVT1-mkbl2.c b/sd_fuse/V310-EVT1-mkbl2.c

new file mode 100755

index 0000000..f754f9f

--- /dev/null

+++ b/sd_fuse/V310-EVT1-mkbl2.c

@@ -0,0 +1,99 @@

+/*

+ * Copyright (c) 2010 Samsung Electronics Co., Ltd.

+ * http://www.samsung.com/

+ *

+ * This program is free software; you can redistribute it and/or modify

+ * it under the terms of the GNU General Public License version 2 as

+ * published by the Free Software Foundation.

+ */

+

+#include <stdio.h>

+#include <string.h>

+#include <stdlib.h>

+

+int main (int argc, char *argv[])

+{

+ FILE *fp;

+ unsigned char src;

+ char *Buf, *a;

+ int BufLen;

+ int nbytes, fileLen;

+ unsigned int checksum = 0;

+ int i;

+

+ if (argc != 4)

+ {

+ printf("Usage: mkbl1 <source file> <destination file> <size> \n");

+ return -1;

+ }

+

+ BufLen = atoi(argv[3]);

+ Buf = (char *)malloc(BufLen);

+ memset(Buf, 0x00, BufLen);

+

+ fp = fopen(argv[1], "rb");

+ if( fp == NULL)

+ {

+ printf("source file open error\n");

+ free(Buf);

+ return -1;

+ }

+

+ fseek(fp, 0L, SEEK_END);

+ fileLen = ftell(fp);

+ fseek(fp, 0L, SEEK_SET);

+/*

+ if ( BufLen > fileLen )

+ {

+ printf("Usage: unsupported size\n");

+ free(Buf);

+ fclose(fp);

+ return -1;

+ }

+*/

+ //nbytes = fread(Buf, 1, BufLen, fp);

+ if(BufLen > fileLen)

+ nbytes = fread(Buf, 1, fileLen, fp);

+ else

+ nbytes = fread(Buf, 1, BufLen, fp);

+/*

+ if ( nbytes != BufLen )

+ {

+ printf("source file read error\n");

+ free(Buf);

+ fclose(fp);

+ return -1;

+ }

+*/

+ fclose(fp);

+

+ for(i = 0;i < (14 * 1024) - 4;i++)

+ {

+ checksum += (unsigned char)(Buf[i]);

+ }

+ *(unsigned int*)(Buf+i) = checksum;

+

+ fp = fopen(argv[2], "wb");

+ if (fp == NULL)

+ {

+ printf("destination file open error\n");

+ free(Buf);

+ return -1;

+ }

+

+ a = Buf;

+ nbytes = fwrite( a, 1, BufLen, fp);

+

+ if ( nbytes != BufLen )

+ {

+ printf("destination file write error\n");

+ free(Buf);

+ fclose(fp);

+ return -1;

+ }

+

+ free(Buf);

+ fclose(fp);

+

+ return 0;

+}

(END)sd_fusing.sh is used to burn uboot and bl2.bin onto SD cards.

diff --git a/sd_fuse/tiny4412/sd_fusing.sh b/sd_fuse/tiny4412/sd_fusing.sh

new file mode 100755

index 0000000..e5e6cdb

--- /dev/null

+++ b/sd_fuse/tiny4412/sd_fusing.sh

@@ -0,0 +1,91 @@

+#

+# Copyright (C) 2011 Samsung Electronics Co., Ltd.

+# http://www.samsung.com/

+#

+# This program is free software; you can redistribute it and/or modify

+# it under the terms of the GNU General Public License version 2 as

+# published by the Free Software Foundation.

+#

+####################################

+

+if [ -z $1 ]

+then

+ echo "usage: ./sd_fusing.sh <SD Reader's device file>"

+ exit 0

+fi

+

+if [ -b $1 ]

+then

+ echo "$1 reader is identified."

+else

+ echo "$1 is NOT identified."

+ exit 0

+fi

+

+####################################

+#<verify device>

+

+BDEV_NAME=`basename $1`

+BDEV_SIZE=`cat /sys/block/${BDEV_NAME}/size`

+

+if [ ${BDEV_SIZE} -le 0 ]; then

+ echo "Error: NO media found in card reader."

+ exit 1

+fi

+

+if [ ${BDEV_SIZE} -gt 32000000 ]; then

+ echo "Error: Block device size (${BDEV_SIZE}) is too large"

+ exit 1

+fi

+

+####################################

+# check files

+

+E4412_SPL=../../spl/u-boot-spl.bin

+E4412_UBOOT=../../u-boot-dtb.bin

+MKBL2=../mkbl2

+

+if [ ! -f ${E4412_UBOOT} ]; then

+ echo "Error: u-boot.bin NOT found, please build it & try again."

+ exit -1

+fi

+

+if [ ! -f ${MKBL2} ]; then

+ echo "Error: can not find host tool - mkbl2, stop."

+ exit -1

+fi

+

+#<make bl2>

+${MKBL2} ${E4412_SPL} bl2.bin 14336

+

+####################################

+# fusing images

+

+signed_bl1_position=1

+bl2_position=17

+uboot_position=81

+

+#<BL1 fusing>

+echo "---------------------------------------"

+echo "BL1 fusing"

+dd iflag=dsync oflag=dsync if=./E4412_N.bl1.bin of=$1 seek=$signed_bl1_position

+

+#<BL2 fusing>

+echo "---------------------------------------"

+echo "BL2 fusing"

+dd iflag=dsync oflag=dsync if=./bl2.bin of=$1 seek=$bl2_position

+

+#<u-boot fusing>

+echo "---------------------------------------"

+echo "u-boot fusing"

+dd iflag=dsync oflag=dsync if=${E4412_UBOOT} of=$1 seek=$uboot_position

+

+#<flush to disk>

+sync

+

+####################################

+#<Message Display>

+echo "---------------------------------------"

+echo "U-boot image is fused successfully."

+echo "Eject SD card and insert it again."

+The transplantation is complete.

Compile

./make.sh

Burn write

./run.sh

Burn uboot into the sd card.

Subsequently, uImage, ramdisk.img and exynos 4412-tiny4412.dtb are copied into the SD card (after burning uboot on linux with script, insert the SD card into windows and copy the three files directly into the SD card). The download addresses of the three files are as follows: http://files.cnblogs.com/files/AP0904225/tiny4412-test-image.tar.gz

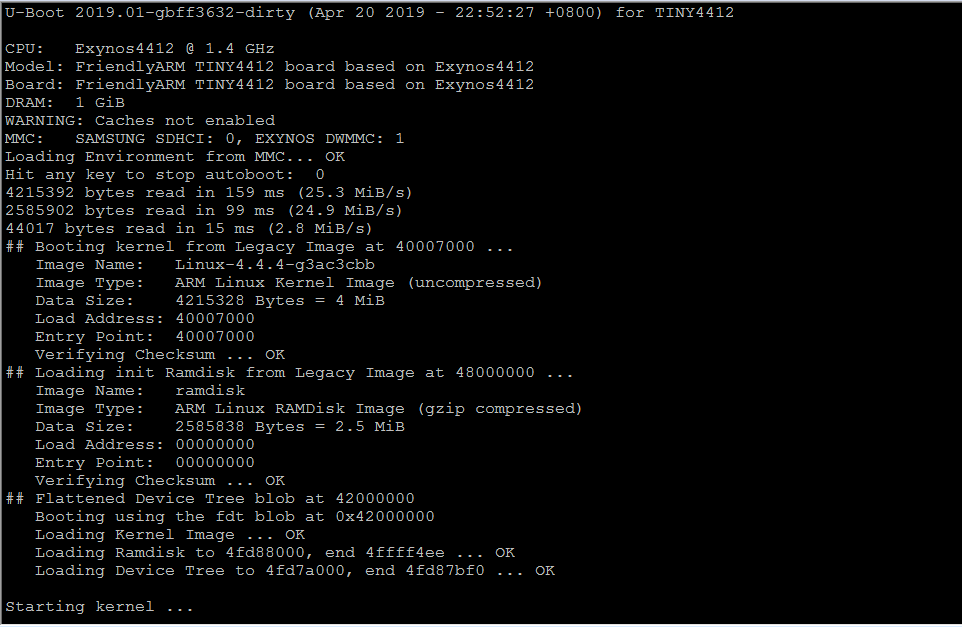

Power-on test, uboot 2019 ran, and started the kernel.

Reference resources: https://www.cnblogs.com/pengdonglin137/p/5080645.html

https://www.cnblogs.com/LoTGu/category/872380.html

https://blog.csdn.net/qq_33160790/article/category/7117737