gcc compiles a single file. makefile can compile a single file or multiple files according to programming rules. Refer to the videos on the network and the posts of great God, and sort out the following that you will use.

makefile basic syntax:

1, Syntax format:

Goal: dependency

(tab) command

Example 1:

all:

gcc test1.c -o test1

Example 2: (clean: delete the. o file and test1 executable file generated by compilation)

all:test1.o gcc test1.o -o test1 test1.o:test1.c gcc -c test1.c clean: rm -rf *.o test1

2, Declare "pseudo target"

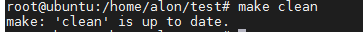

If the make target is duplicate with the file name under the path, the compilation will make an error, as follows:

At this time, you need to declare the pseudo target

Format:

. PHONY: target

all:

gcc test1.c -o test1

.PHONY:clean

clean:

rm -rf *.o test13, Assignment:

1. '=': assign the last specified value

2.'?=': If there is an assignment in front, assign the previous value; if there is no assignment, assign the current value

3. ': =': direct assignment and current value assignment

4. '+ =': additional assignment (note that there is a space in the middle of the output variable)

Example: '='

var1=aaa

var2=$(var1)bbb

var1=ccc

all:

echo $(var2)

output cccbbbExample: '? ='

var1=aaa

var2=$(var1)bbb

var1?=ccc

all:

echo $(var2)

output aaabbb,Because the front has been right var1 Assigned, so var1=ccc No assignmentExample: ': ='

var1:=aaa

var2=$(var1)bbb

var1:=ccc

all:

echo $(var2)

output aaabbb,Because it's executing var2=$(var1)bbb Before, it was executed var1:=aaa,Assign values immediately at this point.Example: '+ ='

var1:=aaa

var2=$(var1)bbb

var1+=ccc

all:

echo ${var2}

output'aaa cccbbb'4, Predefined variables & wildcards

'$<': first dependent file name

'$@': the full name of the target

'$^': all dependencies corresponding to the target

'%': wildcard

Example:

var:=hello.o main.o

hello.o:$(var)

gcc -o $(var) hello # Here $(var) can be replaced with '$^', which represents the list of dependent files, that is, hello.o main.o above

# gcc -o $^ hello

%.o:%.c # %. o stands for all. o, hello.o,main.o

# %. c stands for all. c, hello.c, main.c

gcc -c $^ -o $@ # $^ represents the first dependency, hello.c, main.c

# $@ represents all goals

#######Above makefile It can be interpreted as the following#################################

var:=hello.o main.o

hello.o:hello.o main.o

gcc -o hello.o main.o hello

hello.o:hello.c

gcc -c hello.c -o hello.o

main.o:main.c

gcc -c main.c -o main.o

~

5, Functions

1.wildcard function

Function: expand the specified directory. If there are multiple directories, separate them with spaces

Format: $(wildcard PATTENR)

There is a.c in the test directory and b.c in the test/test1 directory. Now expand the directory to get the. c file

var=$(wildcard ./*.c ./test1/*.c)

all:

echo $(var)

implement make obtain

root@ubuntu:/home/alon/test# make

echo ./a.c ./test1/b.c

./a.c ./test1/b.c

2.notdir function

Function: remove path

Format: $(notdir $(var))

1. In the example of wildcard function, we get the paths of. / a.c and. / test1/b.c. now we need to use this command to get the file names of these two files

var=$(wildcard ./*.c ./test1/*.c)

var1=$(notdir $(var))

all:

@echo $(var1)

implement make We get

root@ubuntu:/home/alon/test# make

a.c b.c

3.dir command

Function: print directory

Format: $(dir $(var))

var=$(wildcard ./*.c ./test1/*.c)

var1=$(notdir $(var))

var2=$(dir $(var))

all:

@echo $(var2)

implement make obtain

root@ubuntu:/home/alon/test# make

./ ./test1/

4.patsubst command

Function: replace file suffix (do not replace source file suffix)

Format: $(patsubst source file, target file, source file list)

var=$(wildcard ./*.c ./test1/*.c)

var1=$(notdir $(var))

var2=$(dir $(var))

var3=$(patsubst %.c,%.s,$(var))

all:

@echo $(var3)

implement make obtain

root@ubuntu:/home/alon/test# make

./a.s ./test1/b.s

ls Take a look at the original order.c The file has not been changed

root@ubuntu:/home/alon/test# ls ./*.c ./test1/*.c

./a.c

./test1/b.c:

5.foreach function

Format: $(foreach < var >, < list >, < text >)

Function: take out the words in the parameter < list > one by one, put them into the variable specified by the parameter < var >, and then execute the expression contained in < text >.

var=$(wildcard ./*.c ./test1/*.c)

var1=$(notdir $(var))

var2=$(dir $(var))

var3=$(patsubst %.c,%.s,$(var))

var4=$(foreach n,$(var2),$(wildcard $(n)*.c)) # The value of $(var2) to n is the path between a.c and b.c, that is. /. / test1/

# Then execute the wildcard command to expand all. c files in the n path

all:

@echo $(var4)

implement make Look at the results

root@ubuntu:/home/alon/test# make

./a.c ./test1/b.c